Paging

Memory management technique using fixed-length blocks.

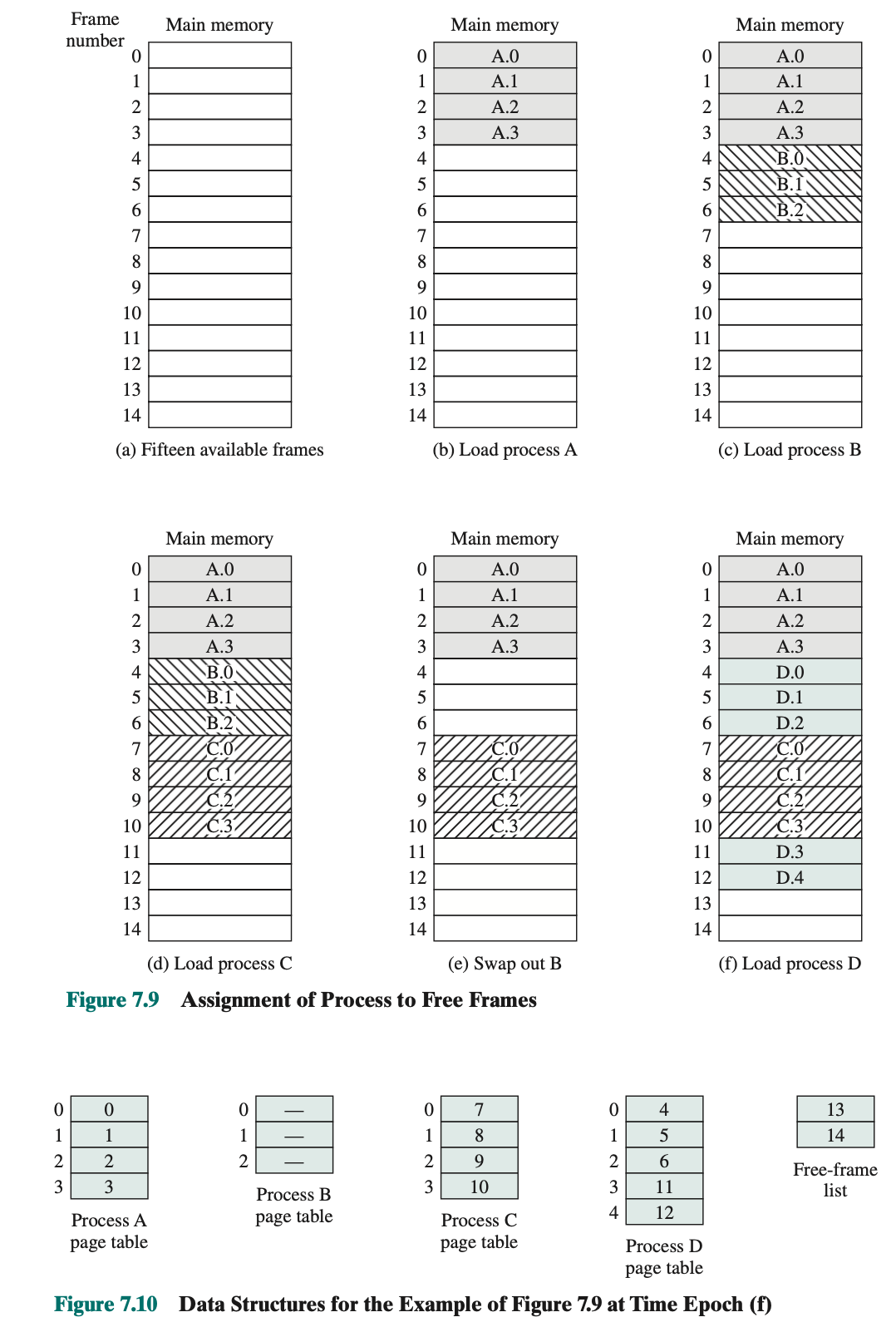

The Main Memory is partitioned into equal fixed-size chunks that are relatively small, and that each process is also divided into small fixed-size chunks of the same size.

The chunks of a process, known as pages, could be assigned to available chunks of memory, known as frames, or page frames.

A list of free frames is maintained by the OS.

Example

Now suppose, as in this example, that there are not sufficient unused contiguous frames to hold the process. Does this prevent the operating system from loading D? The answer is no, we use the concept of logical address. A simple base address register will no longer suffice. Rather, the operating system maintains a page table for each process. The page table shows the frame location for each page of the process. Within the program, each logical address consists of a page number and an offset within the page. Recall that in the case of simple partition, a logical address is the location of a word relative to the beginning of the program; the processor translates that into a physical address.

With paging, the logical-to-physical address translation is still done by processor hardware. Now the processor must know how to access the page table of the current process. Presented with a logical address (page number, offset), the processor uses the page table to produce a physical address (frame number, offset).

Page Table

A page table contains one entry for each page of the process, so that the table is easily indexed by the page number (starting at 0).

Each page table entry contains the number of the frame in main memory, if any, that holds the corresponding page. The OS maintains a single free-frame list of all the frames in main memory that are currently unoccupied and available for pages.

Consequences of using page size that is a power of 2:

- Each logical address (page number, offset) of a program is identical to its relative address. It is a relatively easy matter to implement a function in hardware to perform dynamic address translation at run time