Interrupts

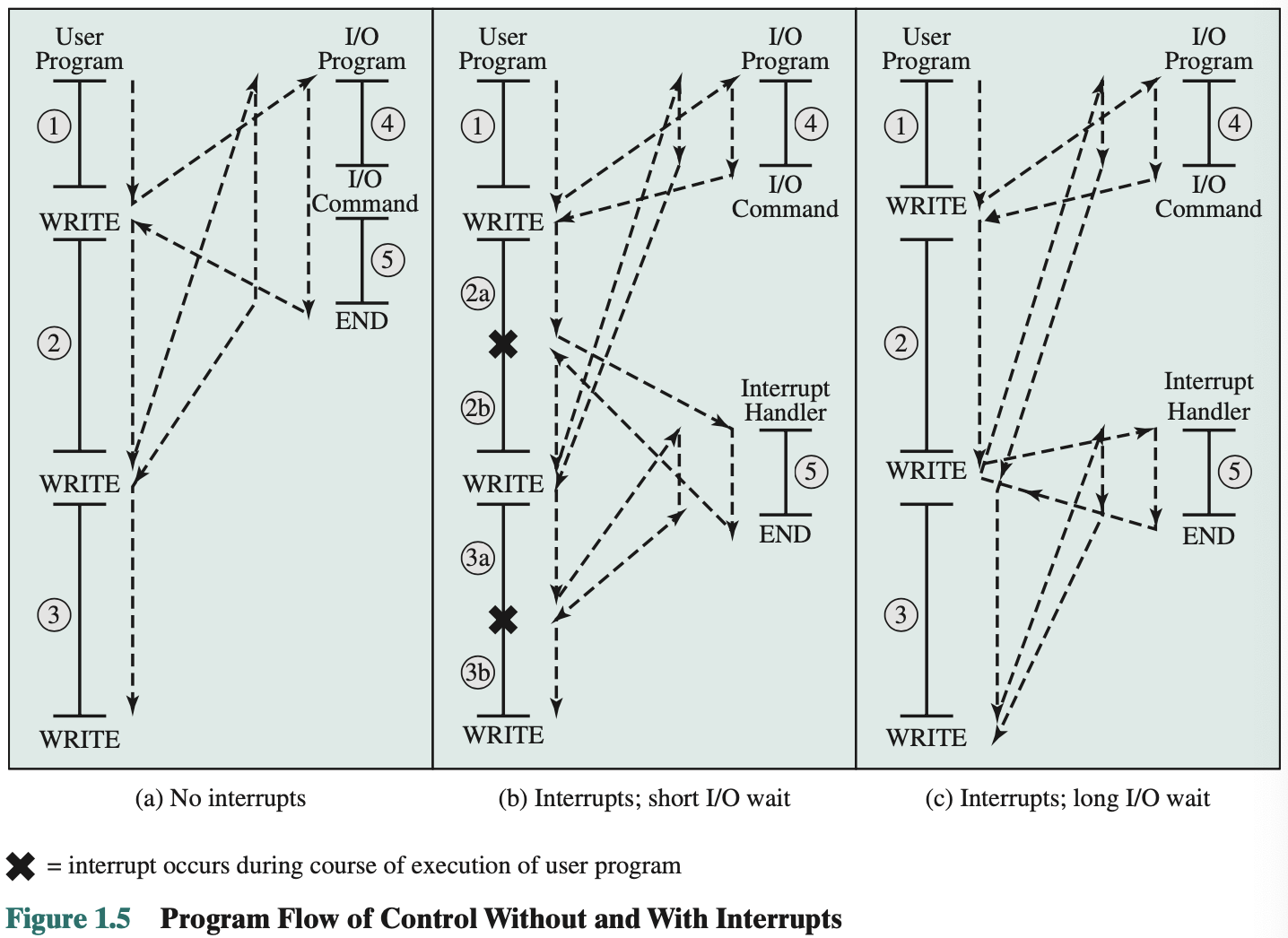

Virtually all computers provide a mechanism by which other modules (I-O Modules, memory) may interrupt the normal sequencing of the processor.

Helps with performance but makes programming complicated.

- Most I/O devices are slower than the Processor

- Processor must pause to wait for device

- Interrupts help to improve the processor utilization

- The change the normal sequencing of the processor

Interrupt Processing

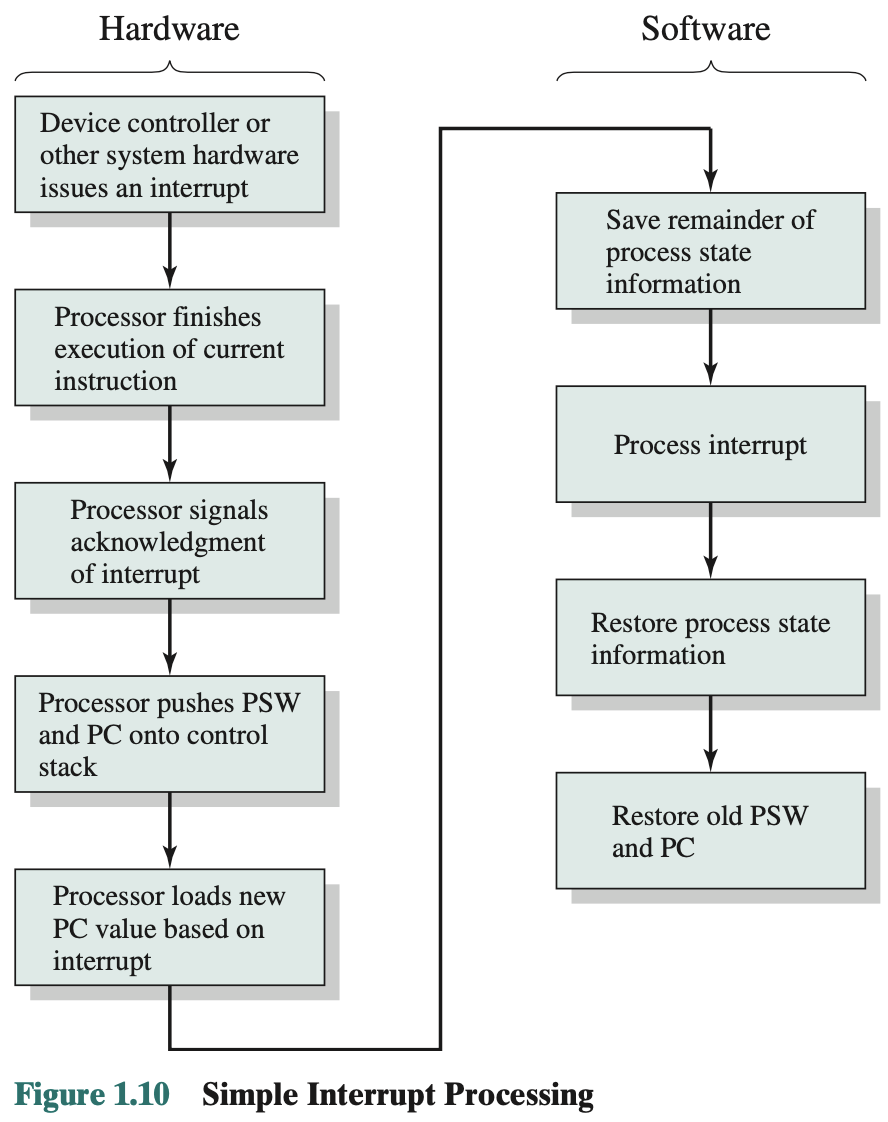

An interrupt triggers a number of events, both in the processor hardware and in software. Figure 1.10 shows a typical sequence. When an I/O device completes an I/O operation, the following sequence of hardware events occurs:

- The device issues an interrupt signal to the processor.

- The processor finishes execution of the current instruction before responding to the interrupt, as indicated in Figure 1.7.

- The processor tests for a pending interrupt request, determines that there is one, and sends an acknowledgment signal to the device that issued the inter- rupt. The acknowledgment allows the device to remove its interrupt signal.

- The processor next needs to prepare to transfer control to the interrupt rou- tine. To begin, it saves information needed to resume the current program at the point of interrupt. The minimum information required is the program sta- tus word3 (PSW) and the location of the next instruction to be executed, which

- The processor then loads the program counter with the entry location of the interrupt-handling routine that will respond to this interrupt. Depending on the computer architecture and OS design, there may be a single program, one for each type of interrupt, or one for each device and each type of interrupt. If there is more than one interrupt-handling routine, the processor must de- termine which one to invoke. This information may have been included in the original interrupt signal, or the processor may have to issue a request to the device that issued the interrupt to get a response that contains the needed information.

Once the program counter has been loaded, the processor proceeds to the next instruction cycle, which begins with an instruction fetch. Because the instruction fetch is determined by the contents of the program counter, control is transferred to the interrupt-handler program. The execution of this program results in the following operations:

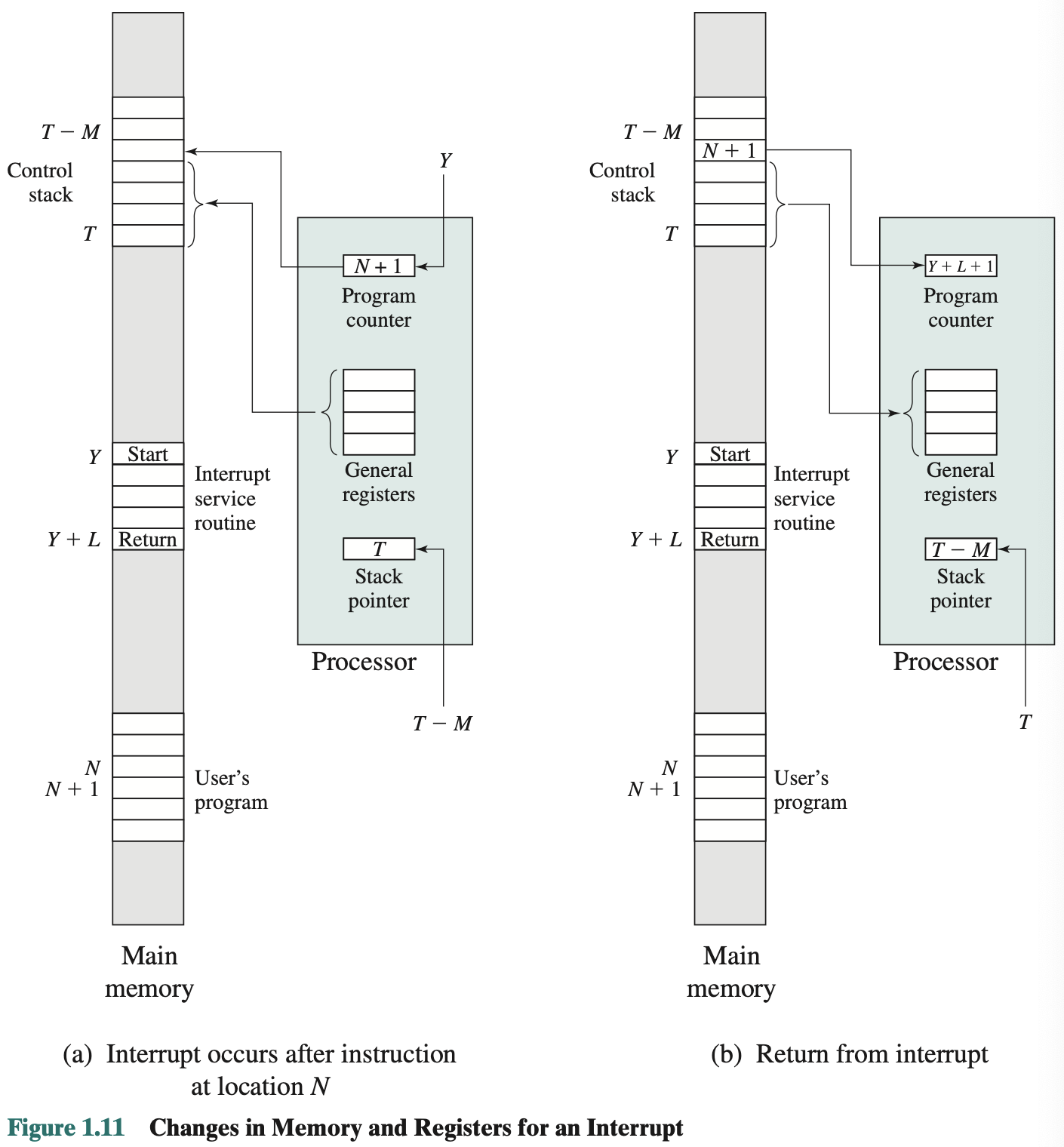

- At this point, the program counter and PSW relating to the interrupted program have been saved on the control stack. However, there is other in- formation that is considered part of the state of the executing program. In particular, the contents of the processor registers need to be saved, because these registers may be used by the interrupt handler. So all of these values, plus any other state information, need to be saved. Typically, the interrupt handler will begin by saving the contents of all registers on the stack. Other state information that must be saved is discussed in Chapter 3. Figure 1.11a shows a simple example. In this case, a user program is interrupted after the instruction at location N. The contents of all of the registers plus the address of the next instruction 1N + 12, a total of M words, are pushed onto the control stack. The stack pointer is updated to point to the new top of stack, and the program counter is updated to point to the beginning of the interrupt service routine.

- The interrupt handler may now proceed to process the interrupt. This includes an examination of status information relating to the I/O operation or other event that caused an interrupt. It may also involve sending additional commands or acknowledgments to the I/O device.

- When interrupt processing is complete, the saved register values are retrieved from the stack and restored to the registers (e.g., see Figure 1.11b).

- The final act is to restore the PSW and program counter values from the stack. As a result, the next instruction to be executed will be from the previously interrupted program.

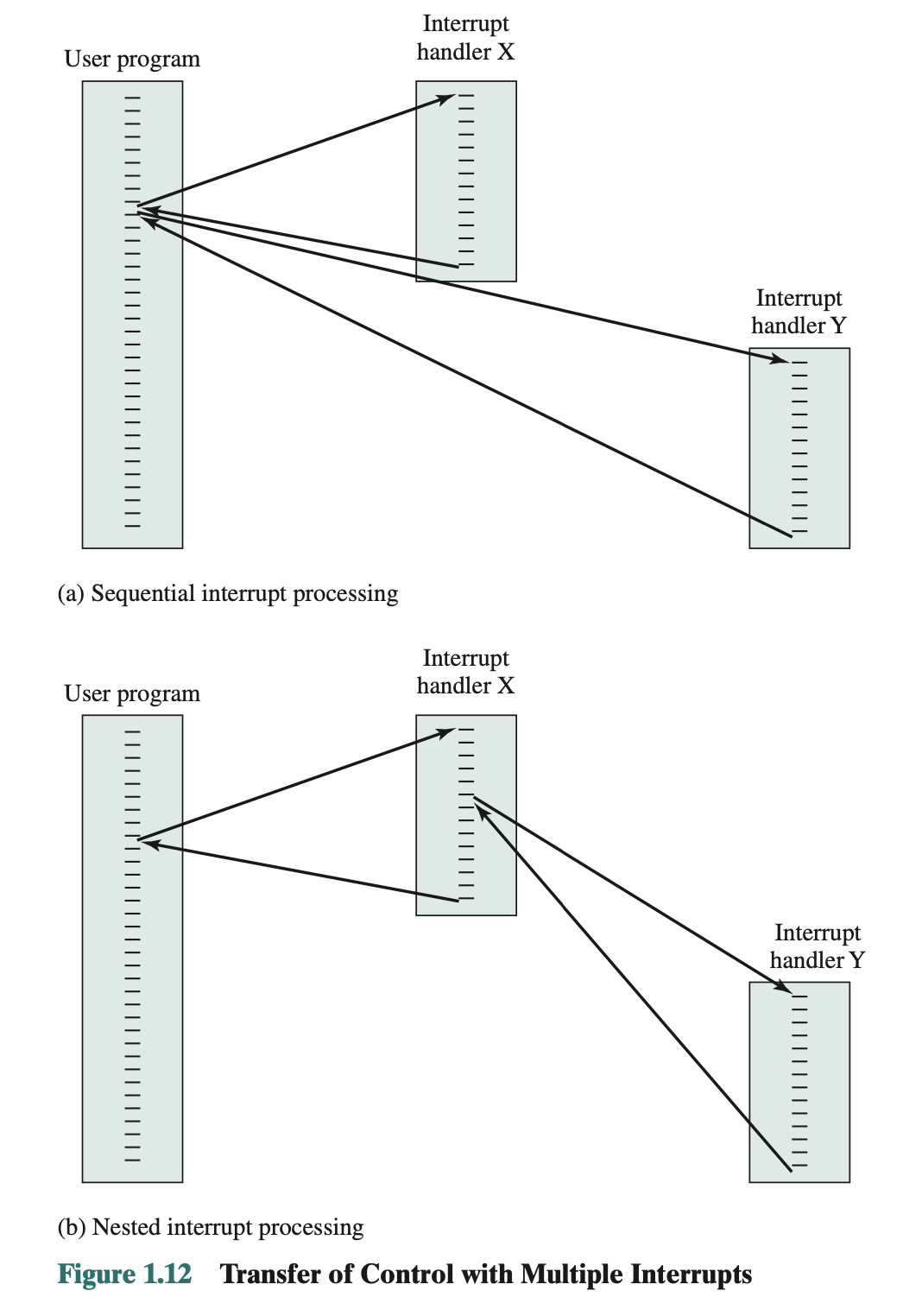

Multiple Interrupts

Explained very well in the book.

First approach is to disable interrupts while an interrupt is being processed. A disabled interrupt simply means that the processor ignores any new interrupt request signal.

Second approach is to define priorities for interrupts and to allow an interrupt of higher priority to cause a lower-priority interrupt handler to be interrupted.